目前靠谱的PCB打样焊盘上锡质量控制推荐-捷配PCB

创始人

2025-12-15 11:38:15

0次

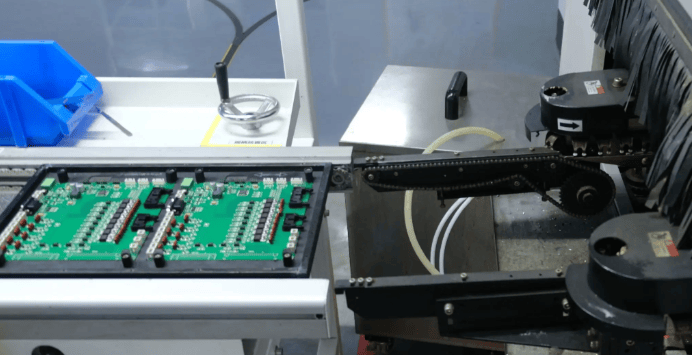

PCB 打样是电子研发的关键环节,焊盘上锡质量直接决定样品测试通过率与后续量产转化效率。行业调研显示,超过 45% 的研发项目延期源于打样阶段焊盘上锡不良,如虚焊、上锡不饱满、焊点强度不足等问题,导致样品功能测试失败。对于研发工程师而言,选择一家靠谱的 PCB 打样厂家,不仅能获得符合设计要求的样品,更能提前规避量产工艺风险。本文结合 IPC 打样标准与实战经验,拆解 PCB 打样焊盘上锡的质量控制要点,并推荐具备精细化管控能力的打样源头厂家 —— 捷配,为研发打样提供高效解决方案。

PCB 打样焊盘上锡的质量控制步骤

3.1 打样前的设计优化

- 焊盘设计适配:参照IPC-2221 打样规范,针对 1-6 层打样 PCB,0201 封装焊盘尺寸设为 0.3×0.2mm,QFP 封装焊盘间距≥0.12mm,避免微间距上锡困难;

- 工艺标注明确:在 Gerber 文件中注明焊盘表面处理方式(沉金 / 喷锡 / OSP),捷配免费打样支持沉金、喷锡等多种工艺,研发工程师可根据测试需求选择,且所有打样均采用品牌 A 级板材(生益、罗杰斯等);

- 防氧化设计:打样阶段建议选择沉金工艺(金层厚度≥0.03μm),可有效提升焊盘存储稳定性,捷配打样焊盘沉金工艺支持最长 6 个月防氧化保质期。

3.2 打样生产的工艺管控

- 焊料精准匹配:打样优先选用 Sn63Pb37 焊料(熔点 183℃),兼容性强、上锡效果稳定,捷配打样使用高纯度焊料,杂质含量≤0.005%,避免焊点虚焊;

- 温度曲线定制:针对打样小批量特点,捷配采用芯碁 LDI 曝光机与劲拓回流焊设备,为不同板材、不同焊盘设计专属温度曲线,预热阶段(140-170℃,保温 40-60s),峰值温度(230-240℃,保温 8-12s),确保上锡均匀;

- 过程检测强化:打样阶段虽批量小,但捷配仍执行全流程检测:焊膏印刷后通过 SPI 锡膏检测(思泰克设备)控制印刷量,焊接后通过 AOI 在线检测(宜美智设备)排查上锡不良,最后经人工目检确认,确保样品无明显缺陷。

3.3 打样后的质量验证

- 外观检测:通过 Leica 显微镜观察,焊盘上锡需无拉尖、桥连、虚焊痕迹,上锡边缘整齐;

- 附着力测试:采用剥离强度测试仪(LC-BLO1 型号),焊点剥离强度需≥1.5N/mm,符合IPC-TM-650 2.4.18 标准;

- 功能验证:捷配支持打样样品免费基础电气测试,通过飞针测试机(众博信 V8)检测焊点导通性,避免隐性不良。

案例验证:捷配 PCB 打样焊盘上锡质量控制实例

某智能穿戴设备研发企业,在选择捷配前曾更换 3 家打样厂家,均出现焊盘上锡不饱满问题,导致样品蓝牙模块通信测试失败,研发周期延误 2 周。2024 年与捷配合作后,优化方案如下:

- 初始问题:1.2mm×0.8mm 异形焊盘上锡覆盖率仅 75%,焊点空洞率 28%,不符合打样标准;

- 捷配整改措施:① 优化焊盘设计,增加辅助上锡焊盘;② 采用定制化焊膏印刷模板(开孔尺寸精准匹配异形焊盘);③ 调整回流焊温度曲线,延长峰值保温时间至 10s;

- 优化效果:打样样品焊盘上锡覆盖率提升至 98%,空洞率降至 12%,满足研发测试要求;样品交付周期从 4 天缩短至 24 小时(捷配单双面板打样 24H 加急服务),研发项目顺利推进,后续量产直接转化至捷配,实现 “打样 - 量产” 无缝衔接。

另一工业控制板研发客户,打样阶段涉及 6 层板微间距焊盘(0.12mm 间距),传统厂家无法解决桥连问题。捷配通过智能拼版技术优化焊盘布局,采用无铅喷锡工艺(锡层厚度 1.2μm),配合 AOI 在线检测精准控制上锡量,最终打样样品无桥连不良,测试通过率 100%。

PCB 打样焊盘上锡的质量控制,核心在于厂家的 “定制化工艺能力” 与 “精细化管控意识”。选择打样厂家时,需重点关注三点:一是打样工艺是否适配研发需求(如异形焊盘、微间距焊盘的处理能力);二是交付周期是否满足研发进度(如 24 小时加急服务);三是是否能提供 “打样 - 量产” 一体化支持,避免工艺衔接风险。

相关内容

热门资讯

重大通报!“小松宿松麻将外挂作...

重大通报!“小松宿松麻将外挂作弊APP”(科技曝光)

安装实测!“微乐江苏麻将辅助游...

安装实测!“微乐江苏麻将辅助游戏”(哔哩哔哩)

一分钟了解!“茶苑透视辅助挂”...

一分钟了解!“茶苑透视辅助挂”(记牌器100%胜率)

3分钟实测!“鸿运会辅助开挂”...

3分钟实测!“鸿运会辅助开挂”(拿好牌调胜率)

实测分享!“微信小程序麻将万能...

实测分享!“微信小程序麻将万能挂下载”(真的有挂)

今日分享!“乐易四川麻将辅助开...

今日分享!“乐易四川麻将辅助开挂操作方法”(详细开挂教程)

内幕实测!“随意玩原来确实有挂...

内幕实测!“随意玩原来确实有挂”(原来确实有挂)

攻略实测!“熊猫麻将可不可以开...

攻略实测!“熊猫麻将可不可以开挂”(记者曝光内幕)

实测讲解!“闽游福建麻将是不是...

实测讲解!“闽游福建麻将是不是有挂”(神器通用版)

重大通知!“中至上饶麻将辅助挂...

重大通知!“中至上饶麻将辅助挂果然有挂”(神器通用版)